|

|

|

| ||

|

| ||

Presentation Slides: all seven presentations in a ZIP file (9.5 MB)

You may stream the seven talks (each about 20 minutes) -- may involve downloading/installing a WebEx player app:

- Talk 1 ("Router Failures")

- Talk 2 ("SER Issues for Advanced Silicon")

- Talk 3 ("Fully Processed Silicon Wafers")

- Talk 4 ("Ultralow Alpha-Emitting Solder Materials")

- Talk 5 ("Thermal Neutrons")

- Talk 6 ("Alpha Emitting Isotope Migration")

- Talk 7 ("Passivation Interconnect Layer")

Thursday, October 28, 2010

Please register in advance for this IEEE Workshop, using our IEEE Council's DoubleKnot registration site.

|

You may register yourself, plus others from your company/institution, for either the live presentation at Cisco Systems, or for the live Webinar over the Internet. As a free event, there is no registration charge. |

PLEASE RESERVE IN ADVANCE -- through Oct. 25 (Monday)

PLEASE RESERVE IN ADVANCE -- through Oct. 25 (Monday)

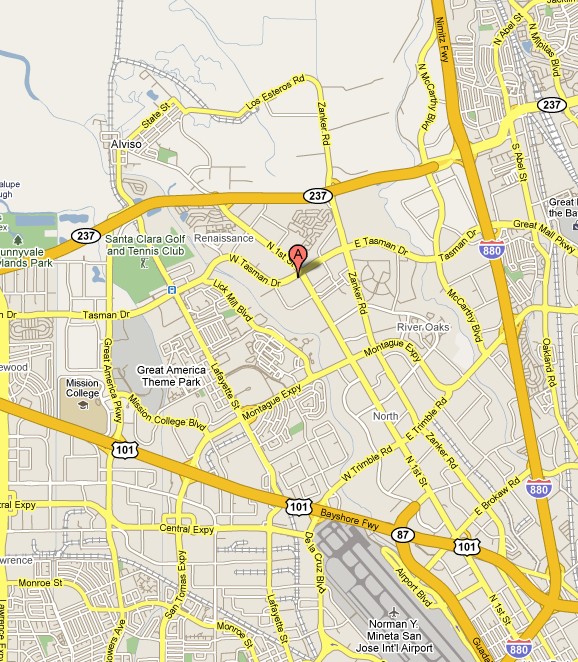

Location:

Cisco Systems, Inc.

|

"Alpha Emission-Induced Router Failures: Diagnosis and Resolution"

Cisco reported that an end customer is experiencing ~600 FIT field failure rate with network routers in a wafer fab. Failure signature is silent re-boot. The silent re-boot failure mode occurs randomly and is indiscriminate with respect to location and time.

Failure signature and FIT rate were reproduced using a high energy neutron beam to accelerate the collision of radiation particles in a well controlled environment. A focused neutron beam was then able to identify a DC-DC converter IC as the only component on Cisco�s router that consistently induced the reboot incident at a rate of ~600 FIT. Direct alpha irradiation was attempted and successfully recreated the same failure signature on a customer returned router. Evaluation boards were used to validate and identify the error source. Light Induced Voltage Alterations (LIVA) was shown to be able to induce the same error waveform. Thus further isolation of error originating circuitry is possible by selectively disturbing specific die locations. BG_BUF (Bandgap Buffer) block was identified as the most likely origin of the PGOOD error waveform. This talk will explore lessons learned and tools utilized to obtain resolution of this incident. The need to understand the effects of radiation on commercial/industrial devices are necessary in keeping with customer�s ever increasing quality expectations |

Chiate Lin joined Intersil in 2008 as Staff Reliability Engineer. He is responsible for ensuring Intersil's consumer and industrial power products meet or exceed customers' quality and reliability expectations. Before Intersil, he was Corporate Reliability Manager for Inapac Technology Inc., a KGD DRAM SiP company, from 2003 to 2008. he served as Technology Manager at Magis Networks responsible for its foundry operations from 2001 to 2003. Prior to Magis, Chiate was a Senior Foundry Engineer at Qualcomm CDMA Technologies (QCT) from 1997 to 2001 working with IBM Microelectronics and TSMC on RFICs and digital baseband ASICs. He received his Bachelor of Science degree in Electrical Engineering from University of California, San Diego. |

| "A Systematic and Collaborative Approach to Address SER Issues for Advanced Silicons" With each new fabrication technology, mechanisms affecting SER become more complex. With increased IC fabrication cost, SER evaluations through design, fabrication, and testing of ICs is fast becoming an expensive proposition. A collaborative, cost-effective approach is developed for a 28-nm technology-evaluation test IC between 7 semiconductor companies and Vanderbilt University. The main hurdles for such an effort are issues related to legal, logistical, design, confidentiality, and testing. Such an approach can be a blueprint for future technology nodes to evaluate reliability concerns during early stages of process and product development. | Professor Bharat Bhuva is with the Department of Electrical Engineering & Computer Science at Vanderbilt University. Hi has been involved with radiation-effects on semiconductor devices and circuits for the past twenty years. He has published over 150 papers over the years, and has developed software tools related to soft-error evaluations ranging from TCAD level to system-level. He also has designed multiple test ICs for evaluation of soft-error related mechanisms. |

| "Alpha Emission of Fully Processed Silicon Wafers" Measured alpha particle emissions from packaging materials have been used to calculate the Soft Error Rate of silicon components. The packaging materials have been assumed to be the only alpha emitter and the layers on top of the silicon have been assumed to be the alpha attenuators. This paper measures the alpha emission of the fully processed wafers from different vendors and shows that these wafers are significant alpha emitters. Because the alpha emitters in this case arises very close to the silicon, there are no shielding layers to attenuate the lower energy alpha particle. The entire alpha particle energy spectrum, from both package materials to the as well as inside wafers, must be considered for the alpha flux, when calculating the alpha flux. | Richard Wong received his M.S. degree in electrical engineering from Santa Clara University in 1988 and his B.S. degree in chemical engineering from UC Berkeley in 1982. He joined Cisco Systems Inc., in 2006. He is engaged in IC component technology reliability assurance in issues such as Single Event Upset, Electrostatic Discharge, Wafer Level Reliability, failure analysis and reliability modeling. Prior to Cisco, he had worked on ASICs, FPGAs, TCAMs and memories. |

| "Challenges in Supply and Testing of Ultralow Alpha-Emitting (ULA) Solder Materials" Authors: Dr Andy Mackie, Mark Olearczyk (Indium Corporation) and Olivier Lauzeral (iROC). A supplier of ultralow alpha (ULA) materials, that is, materials with an alpha particle emission of less than 0.002cph/cm2, faces a number of challenges. This paper will describe how Indium Corporation, in association with Alpha Science and iROC, has developed capabilities in the supply of ULA solder pastes, and also goes into the procedural, materials procurement, manufacturing, storage, packaging, OQC and shipment controls critical to success in supplying product to an Asian customer. | Andy C. Mackie is the Global Product Manager for Indium Corporation's Semiconductor Assembly Materials. Andy has over 20 years of experience in new product and process development and materials marketing in all areas of electronics manufacturing. Andy is an electronics industry expert in physical chemistry, surface chemistry, rheology, solder materials properties and processes (including solder paste printing), and reflow. Andy�s industry involvement includes iNEMI, SMTA, IPC, and many others. Andy has a PhD in Physical Chemistry from the University of Nottingham, UK, and a Masters of Science in Surface and Colloid Chemistry from the University of Bristol, UK. |

| "Soft Error Rates Induced by Thermal Nutrons" Soft errors from alpha particles and high-energy cosmic rays are a well recognized source of soft errors in modern ICs. Thermal neutrons are known to be an issue in devices containing boro-phospho-silicate glass (BPSG) due to the large capture cross sections of 10B. Since chem-mechanical polishing (CMP) has replaced BPSG as a planarizing layer in deep sub-micrometer processes, it was commonly believed that soft errors from thermal neutrons would not be an issue. However, recent studies have shown significant thermal neutron soft error rates in IC designs below 150nm. This study estimates alpha particle generation from thermal neutron capture in boron source-drain implants, p-type polysilicon and p-type substrates. | Charles Slayman has been working in quality and reliability of memory technology and soft error mechanisms. He received the Ph.D. degree in electrical engineering and computer science in 1980, and B. A. degree in physics in 1974, both from the University of California at Berkeley/ |

| "A Study of Alpha Emitting Isotope Migration Within Lead-Free Materials" Previous research has discussed migration of alpha-emitting Polonium isotopes within a lead matrix, but no comparable work exists for other materials. The transition to lead-free solders for semiconductor packaging provides the basis to study this potential effect in lead-free materials. Experiments were conducted to measure the alpha emissivity at different positions within a tin material to ascertain the extent to which alpha-emitting isotopes migrate. The results of the experiment and the potential implications to packaging-related soft errors will be discussed. | Dr. Brett Clark manages the Analytical and Metrology Laboratory at Honeywell Electronic Materials in Spokane, Washington. His research areas include liquid particle counting, low level radiation measurement, and materials science of high-purity metals and alloys. He received a Ph.D. degree in physical/analytical chemistry from Brigham Young University, and has authored/coauthored seven journal publications and ten patents. |

| "Alpha Particle Shielding with Cu Post Passivation Interconnect Layer" Flip-chip packaging technology with Sn/Pb bumps is highly susceptible to alpha emission excursion from contamination in the manufacturing process. This paper describes a novel technique to reduce the risk of alpha SER in devices using flip-chip packaging technology. In this work, we have developed a special Cu Post-Passivation Interconnecting layer (Cu-PPI) that act as additional shielding material between the bump and the active layer. Experimentation with accelerated alpha testing was done which shows that the Cu-PPI layer can reduce alpha flux by up to 5X. | Dr. Nelson Tam joined Intel Corporation, where he worked on the development of phase shifting mask. In 1997, he joined the Enterprise Processor Division as a Quality and Reliability Engineer focusing on IPF processor pre-Si reliability verification. In 2006, he jointed Marvell Semiconductor Inc. as a Principal Reliability Engineer focusing on soft error issues. His research interests include simulation and experimental techniques for determining radiation effects on devices, and process and design solutions to mitigate them. Dr. Nelson Tam received the B.S. degree in chemical engineering and the M.S. and Ph.D. degrees in electrical engineering and computer science from the University of California, Berkeley. |

| Final presentation is scheduled to finish at 11:45 AM | |

|

SCV Chapter

Home Page |

How to Join IEEE |

Contact our Chapter Chair |

| CPMT Society

Home Page |

IEEE Home Page |

Email

to Webmaster |

Last updated on